# The COTS Technology Authority EMBEDDED SYSTEMS VOLUME 2 NUMBER 2 SUMMER 2006

IN THIS ISSUE:

#### Mil Tech Trends

Multi-domain modelina pg 34

#### **Product Guide**

Multicore processor boards

pg 42

WWW.MIL-EMBEDDED.COM

Trends in Software-Defined Radios

**EXCLUSIVE INTERVIEW Col. Steven MacLaird** Former JTRS JPO Prog. Exec. Dir.

Can FPGAs replace stand-alone DSPs?

PRST STD U.S. POSTAGE **PAID** BLAINE, WA PERMIT NO. 226

# Keep your SPARC supply lines open.

USP Ile™ VMEbus Computer

650-MHz UltraSPARC<sup>®</sup> IIi+ CPUs 4GB SDRAM

Optional TGA3D+™ and TGA-100™ graphics support Gigabit Ethernet

PCI expansion to four slots

Four serial ports

VME Interface – VME64X via Tundra Universe II PS/2 or USB keyboard/mouse

Solaris™ 8/9/10 Support

USP IIIi™ VMEbus Computer

Two UltraSPARC IIIi

1.2 GHz CPUs

4GB 266DDR SDRAM

per CPU, 8GB total

Optional TGA3D+

and TGA-100 graphics

Gigabit Ethernet port

One 64-bit/66-MHz PMC slot

Up to four PMC expansion slots

Dual FC-AL/SCSI ports

Additional VME-backplane access

Up to 30G shock

Solaris OS Support

Do your mission critical applications depend on SPARC/ Solaris solutions? Many suppliers are ending their support for SPARC-based single board computers. Not Themis. Themis is committed to providing its customers and industry with high performance UltraSPARC VMEbus single board computers.

Themis has solutions. We are committed to providing you with the industry's widest breadth of high performance UltraSPARC-based VME single board computers. To support thousands of Solaris platform solutions for the most demanding mission critical applications.

Don't be forced into changing your computing platform today. Extend the life of your system and gain control over your program lifecycle and budget with Themis SPARC solutions.

Themis is keeping the SPARC supply lines open so call Themis today.

www.themis.com (510) 252-0870

Transformational.

RSC# 2 @www.mil-embedded.com/rsc

# Discover Condor's Avionics Embedded Solutions

It's easy to see why we're the leader.

# 1553 | 429 | AFDX | MMSI

- Rugged and reliable

- High performance

- Advanced FPGA technology

- VxWorks, Integrity, LynxOS

& other RTOS supported

- Test and integration tools

- Intellectual property cores

- ISO 9001:2000 certified

- Outstanding technical support

Go with the leader.

VOLUME 2 NUMBER 2

SUMMER 2006

www.mil-embedded.com

#### **DEPARTMENTS**

#### **Industry Analysis**

8 Has crummy old technology survived?

By Don Dingee

#### **Departments**

10 Editor's Choice Products

51 New Products

By Sharon Schnakenburg

#### **Crosshairs Editorial**

54 What's up with Intel and AMD?

By Chris A. Ciufo

6 Advertiser Index

#### **EVENTS**

#### **MILCOM 2006**

Oct. 23-25, 2006 • Washington, DC www.milcom.org

#### GCDv

Oct. 30-Nov. 2, 2006 • Santa Clara, CA www.gspx.com

# SDR Forum 2006 Software-Defined Radio Technical Conference and Product Exposition

Nov. 13-17, 2006 • Orlando, FL www.sdrforum.org

#### COVER

The U.S. Army's Land Warrior program calls for network-centric assets relying on a *Soldier of One*. Lightweight reconfigurable Joint Tactical Radio System (JTRS) equipment is essential for digital information exchange – depending on critical DSP, FPGA, and COTS software. Related articles appear on pages 12 and 22. (Image courtesy of the U.S. Army)

#### On the cover

The IBM Cell processor implements a 64-bit PowerPC core with eight additional synergistic cores, allowing up to 10 simultaneous threads and more than 128 outstanding memory requests.

Published by:

© Military Embedded Systems

All registered brands and trademarks within *Military Embedded Systems* magazine are the property of their respective owners.

#### **FFATURES**

#### HARDWARE: Reconfigurable FPGAs

- 12 Board vendor FPGA toolkits make or break your project

By Mark Littlefield, Curtiss-Wright Controls Embedded Computing

- 16 Design strategies for an FPGA-based 256-channel digital down converter

By Rodger H. Hosking, Pentek, Inc.

#### **SOFTWARE:** Software-Defined Radios (SDRs)

22 SDR and JTRS: Lessons learned

Q & A with Col. Steven MacLaird, USAF (ret.) and former Program Executive Director of the Joint Tactical Radio System JP0

26 The next advancements in Software-Defined Radio

By Joseph M. Jacob, Objective Interface Systems, Inc.

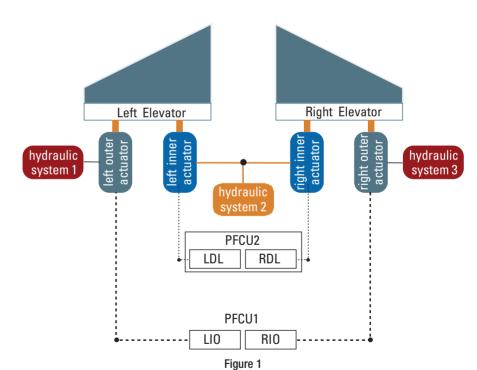

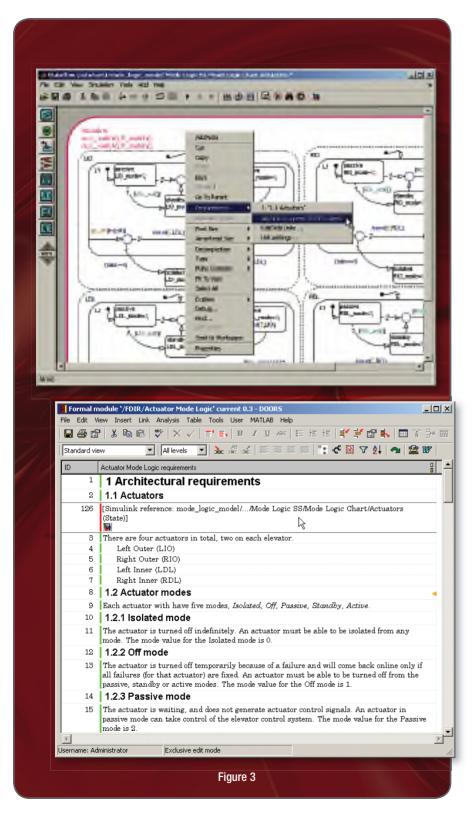

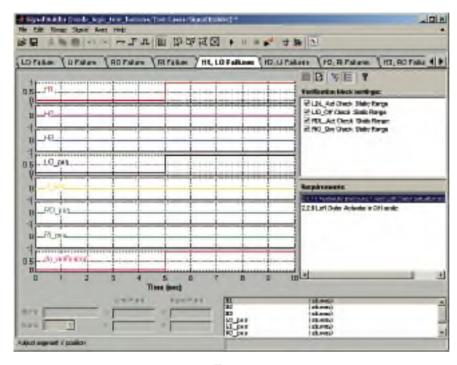

#### MIL TECH TRENDS: Design modeling

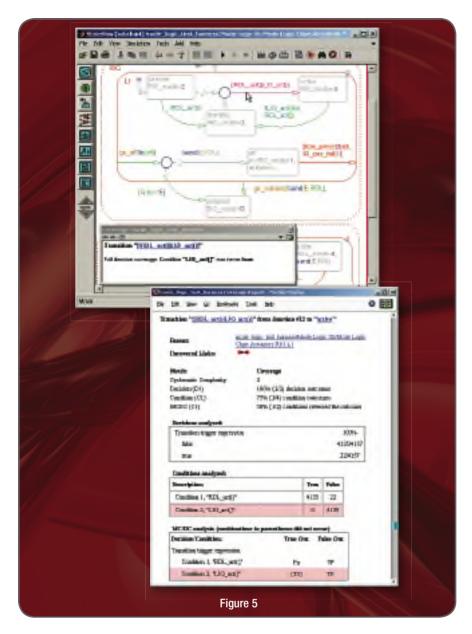

Applying Model-Based Design to a Fault Detection, Isolation, and Recovery system

By Jason Ghidella, PhD, and Pieter J. Mosterman, PhD, The MathWorks, Inc.

#### **PRODUCT GUIDE: Multiprocessors**

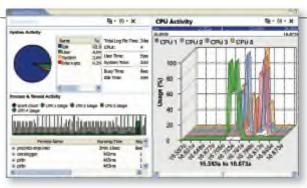

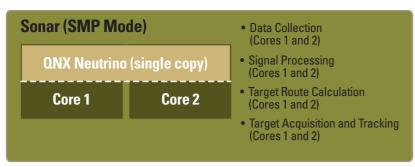

- **Migrating legacy applications to multicore processors** *By Paul Leroux and Robert Craig, PhD, QNX Software Systems*

- 49 Multiprocessor/multicore single board computers and DSP modules

#### **E-LETTER**

# Achieving the full-circle promise of Eclipse-based development tools: A new technology ecosystem of opportunities and risks

By Marc R. Erickson, Communications and Media Arts

Visit us online for the complete list of articles at www.mil-embedded.com/eletter.

#### **WEB RESOURCES**

#### Subscribe to the magazine or E-letter:

www.opensystems-publishing.com/subscriptions

#### **Industry news:**

Read: www.mil-embedded.com/news

Submit: www.opensystems-publishing.com/news/submit

#### Submit new products:

www.opensystems-publishing.com/vendors/submissions/np

# **Advertiser Information**

#### Extreme environments require extreme solutions...

#### Liquid Cooled 100W/Slot 1 ATR

- Brazed construction

- Liquid cooled card cage side walls

- Accepts conduction cooled cards

- Cools up to 100W/slot power dissipation

- 8 Slot VITA 41 VXS or VME64x

- Backplane with custom I/O

- MIL-STD-704 800 Watt power supply

- MIL-STD-461 EMI

www.hybricon.com

Hybricon Corporation 12 Willow Road Ayer, MA 01432 Call Today 1-877-HYBRICON Page/RSC# Advertiser/Product description

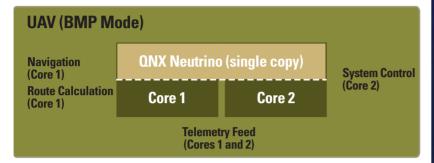

- 52 ACT/Technico PMC Storage

- 48 Advantech Corporation Stackable SBCs

- 17 Annapolis Micro Systems FPGA Systems

- 46 BittWare 6U VME/VXS Board

- 3 Condor Engineering Avionics Embedded Solutions

- 56 Curtiss Wright High-performance Graphics Products

- 2701 Datametrics Rugged Workstations

- 39 DIGITAL-LOGIC Microspace MSM855

- 44 Embedded Planet EP8548A Serial RapidlO AMC

- 31 Excalibur Systems Avionics Communications

- 55 GE Fanuc Embedded Systems Embedded Systems

- 21 General Micro Systems V394, CC61X

- 43 GSPx GSPx Silicon Valley 2006

- 7 Harris RF Communications Division Encryption Modules

- 19 Hunt Engineering USB-connected Programmable FPGA Systems

- 6 Hybricon Liquid-cooled 100 W/Slot 1 ATR

- 33 Hypertronics Ruggedized Connector Solutions

- 9 ICS Sensor Processing ICS-8550

- 5 Intel Military Platforms

- 11 Jacyl Technology Digital FPGA and Analog FPAA

- 45 MILCOM 2006 MILCOM 2006

- 41 Military and Aerospace Electronics Technical Conference and Exhibition 2006

- 53 MPL AG Rugged Embedded Computers

- 3701 North Atlantic Industries Military Power Supplies

- 47 Optima EPS Custom Cabinets/Enclosures

- 2702 Phoenix International Data Storage Modules

- 51 Real-Time Innovations Data-critical Networked Applications

- 28 RTD Embedded Technologies HighRel PC/PCI-104 Modules and Systems

- 2501 TEWS Technologies Embedded I/O Solutions

- 2502 Thales PENTXM2

- 2 Themis Computer SPARC SBCs

- 3702 Tri-M Systems Flash Solutions

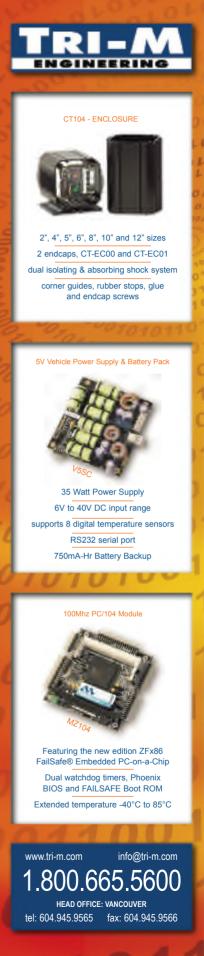

- 35 Tri-M Systems CT104 Enclosure

- 23 VMETRO Real-Time Multiprocessors

ISSN: Print 1557-3222

Military Embedded Systems (USPS 019-288) is published four times a year (Spring, Summer, Fall, Winter) by OpenSystems Publishing LLC, 30233 Jefferson Avenue, St. Clair Shores, MI 48082

Subscriptions are free to persons interested in the design or promotion of *Military Embedded Systems*. For others inside the US and Canada, subscriptions are \$28/year. For 1st class delivery outside the US and Canada, subscriptions are \$50/year (advance payment in US funds required).

Canada: Publication agreement number 40048627

Return address WDS, Station A PO Box 54, Windsor, ON N9A 615  $\,$

POSTMASTER: Send address changes to *Military Embedded Systems* 16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

Take a closer look at your encryption.

Are you getting the protection you need?

Members of the Sierra™ family of encryption modules are easily integrated into communications devices of all kinds. Sierra encrypts classified information, processes data at a higher speed, is extremely power efficient, and allows modules to be reprogrammed as missions change.

It's benefits like these that led the U.S. Department of Defense to select Sierra II for one of the most important communications programs in recent history. Sierra II has been chosen to encrypt 100 percent of the radios under Cluster 1 of the U.S. Joint Tactical Radio System program.

Learn more at www.rfcomm.harris.com.

www.harris.com

Broadcast

Microwave

RF

Government

# **Industry Analysis**

# Has crummy old technology survived?

By Don Dingee

The seminal February 1994 *Mandate for Change* speech called for Commercial Off-the-Shelf (COTS) computing equipment, targeting:

- » Reduced system costs

- » Decreased system design time

- » Improved system performance

- » Reduced dependence on single-source suppliers

- » Combined effects reducing total acquisition costs

Has COTS worked, or has *crummy old technology* survived? There are examples for both sides.

#### **Direct hit**

One case where COTS has gone right is the U.S. Navy's AN/BQQ-10 Acoustic Rapid COTS Insertion (A-RCI) program. A-RCI integrates COTS technology into submarine sonar systems in the Los Angeles SSN-688I class and has greatly increased antisubmarine warfare processing power at the Navy's disposal.

The A-RCI design teams at Lockheed Martin packed more than twice the sonar processing power onto a single sub than existed in the entire submarine fleet theretofore. Living the philosophy of *maximum density*, they traversed several form factors – 6U and 9U VMEbus boards and packaging from various suppliers, 2U rack-mount Pentium servers, even Apple Xserve boards repackaged to fit, looking to pack more processing into each design generation. The result: reduced system costs of about 20 percent over each generation of deployment. This program definitely hit the target intended for COTS.

#### Wide left and wide right

I'm aware of two recent examples of COTS selection that I believe went wrong, for different reasons:

- » The SSGN program converts U.S. Navy ballistic missile submarines to cruise missile firing and special operations deployment capabilities. Its Vertical Launch Subsystem (VLS) called for a VMEbus processor board. During competitive bids in 2002, the prime contractor requested the bill of material for each board. Fifteen obsolete parts were found on the winning board at the time of selection, and the plan was for the U.S. Navy to procure a lifetime inventory for each of those obsolete parts. Buying and storing more and more crummy old technology as the list of obsolete components on a board grows over time doesn't make much sense.

- » The Digital Airport Surveillance Radar (DASR), jointly managed by the U.S. Air Force and Federal Aviation

Administration, detects aircraft position and weather conditions near civilian and military airfields. The ASR-11 – or its analog predecessor – is the large, orange, rotating *cattle gate* seen on the perimeter of most large airfields today. ASR-11 decided to borrow proven COTS technology from the Mode Select Beacon (or Mode-S) program, which completed a successful upgrade to a 68040 VMEbus board between 1998 and 2003. One small problem: By the time ASR-11 started deployment in 2003, the 68040 VMEbus board was ready to retire and finally did in 2004. The selection of *crummy old technology* for a compute engine can be a major setback, even if it feels safer at the time.

#### Old habits die hard

What conditions help COTS computing gear *work* for a program? Three seem to be important:

- Aligned thinking. Directorate and program office teams and the contractor management teams must not only stand behind the concept of COTS but proactively break down traditional bureaucratic barriers and thinking. And vendors need to be involved in the thinking, too.

- 2. Shorter life cycles. Keeping design cycles as short as possible provides greater freedom in selecting computing technology, and planning for faster insertions of new technology keeps the total system life cycle short.

- 3. Fixed scope. Design teams should know more about their scope such as how many units they have to field, when decisions must be made, and when systems must be deployed. This helps contain risks, leverage knowledge from previous design cycles, and succeed while moving forward quickly. If the scope increases, the technology should be able to change.

#### Get off that crummy old technology

Creating any significant change is hard. Vendors, contractors, and the military need to work together to get COTS right more often. COTS board and system vendors are very hard-pressed to satisfy demands for the latest and greatest technology while simultaneously keeping older generations of product alive for what in today's technology cycles can be an epoch. Get off of the old stuff.

Is COTS working for your program or not, and why? We would love to hear from you, and you can reach me at ddingee@ opensystems-publishing.com.

# More Features. More Rugged. More reasons to choose ICS. The one and only ICS-8550.

Designed for high-speed data acquisition applications such as Software Defined Radio, SIGINT, tactical communications and radar, the ICS-8550 XMC module — which is available for both benign and rugged environments — can simultaneously sample two RF/IF inputs at frequencies up to 210 MHz at a resolution of 12 bits.

With the industry-leading Xilinx Virtex-4 FPGA at its heart to deliver unprecedented power and user programmability — and enabling IF/UHF signals to be processed directly on the board itself, freeing the host board for other tasks — the ICS-8550 is truly an ADC module that sets new standards.

And with up to eight lanes of high-speed serial I/O, the ICS-8550 provides the throughput to match its performance and flexibility. Configure it with Radstone's remarkable V4DSPFPGA/PowerPC processor, and the partnership is unbeatable.

ICS. For when you need more.

# Editor's Choice Products

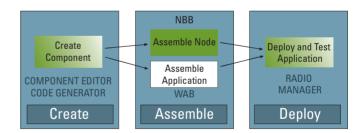

#### JTRS waveforms made <del>easy</del> easier

The DoD's Joint Tactical Radio System (JTRS) is a huge program that

has boatloads of software at its core. Of primary importance are the SCA core framework and the portable waveforms that must work on myriad equipment while interoperating with older, hard-wired radios. Therefore, writing code for JTRS equipment can be a real nightmare. At least, that's the problem that Zeligsoft is trying to solve with its Component Enabler (CE) 2.4. This JTRS development tool helps software designers determine the usability of their software *components* in the field, and verifies compliance against the SCA.

CE 2.4 takes into account the target hardware *deployment platform* that the JTRS radio will ultimately run on. It also allows designers to write code and then iterate that code to balance the metrics of JTRS compliance, hardware choices, and waveform interoperability. Because of the iteration capability, the product speeds development, aids in the test phase, and ultimately saves costs.

Also available in CE 2.4 are modeling, validation, and runtime analysis capabilities. Multiple application views are intended for teams working on different portions of the overall code set, while keeping track of the overall combined set of software modules. A validation feature links to SCA validation and the latest version of the SCA specs, flagging rule violations. Writing and validating code for a JTRS radio will never be easy, but Zeligsoft's Component Enabler makes the task easier.

#### Zeligsoft

www.zeligsoft.com RSC# 30700

#### Rugged 3U CompactPCI SBC

Until the new 3U VITA 46 slim VME form factor becomes a reality later this year,

3U CompactPCl is still the format of choice for retrofitting space-constrained defense systems. With ample I/O capability and a nice size that fits well into ATR boxes and some SEM-E envelopes, 3U CompactPCl is an ideal choice. Aitech Defense Systems agrees, to which their C900 MPC7447A/7448-based PowerPC SBC can attest. Screaming along at 1.167 GHz with AltiVec signal processing support, the board includes up to 1 GB of DDR SDRAM complete with ECC. (Aitech is big into space-based apps, so you'd expect they'd include ECC or other provisions to deal with radiation effects.)

The board also includes 64 MB of user flash and a whopping 1 GB of NAND flash for program stores. There's also a thoughtful 128 kB NVRAM for application variables and 32 MB of boot flash. A Marvell MV64460 Discovery III chipset offers a PCI-to-PCI-X bridge. There's also a PMC mezzanine provision, as well as a bunch of I/O options. Two GbE ports, two USB 2.0 ports, and up to eight discrete I/O channels (or four RS-422 serial channels) round out the "goes-innas and goes-outtas." As you'd expect from Aitech, air- and conduction-cooled versions are available. Betcha they'd even make you one that's rad-hard.

#### **Aitech Defense Systems**

www.rugged.com RSC# 23045

The gazillion gate highly integrated FF from companies ranging from A to X performance to spare but come with a heavy power penalty. Although VME boards have ample power budgets of up to 100 W these days, that power has to be dumped into the sys-

tem somehow. If you can save power, why not do it? That's the intention of QuickLogic's QL8150 Eclipse II FPGAs. Designed for light-density logic applications such as handheld devices, they're also ideal for fixed-function interface controllers on VME basecards, PMC mezzanines, active backplanes, and chassis front panels.

With 188,946 maximum gates and 640 logic cells in a 32 x 32 logic array, this small 8 x 8 mm footprint BGA package uses only 196 fine-pitch balls. Power consumption varies, but think *battery powered* and you're in the right realm. The devices are designed to operate over a -40 °C to +100 °C temperature range, so deployment in conduction-cooled VME chassis should be no problem.

#### QuickLogic

www.quicklogic.com RSC# 30701

# PDA's protective skin saves soldiers' lives

Anyone with an iPod knows that a protective case called a *skin* protects the unit from scuffs and scratches and cushions it for the inevitable drop onto concrete. OtterBox cases protect iPods, tablet PCs, portable GPS units, and myriad other handheld electronic devices. But recently, Otter Products' OtterBox 1900 PDA case has been used to save lives when coupled with an HP iPAQ hx4700.

The company worked with the U.S. Army's Medical Research and Materiel Command's Medical Communication for Combat Casualty Care (MC4) and the Telemedicine and Advanced Technology Research Center (TATRC) to cocoon the iPAQ for battlefield medical needs. TATRC's Battlefield Medical Information System Tactical — Joint (BMIST-J) allows Army tactical medical forces to quickly and securely document patient information at the point of injury. The system replaces the World War II vintage paper DD Form 1380. Without the OtterBox 1900 PDA case, the iPAQ would never survive the rigors of life on the front lines, including moisture, dust, shock, and vibration.

MC4 has deployed more than 12,000 OtterBox and BMIST-J systems, with a savings of more than \$1,000 per unit compared to a purpose-built rugged PDA costing upwards of \$1,500 each. Otter Products also manufactures numerous other protective skins for civilian and custom handhelds.

#### **Otter Products**

www.otterbox.com RSC# 31423

Editor's Choice Products are drawn from OSP's product database and press releases. Vendors may add their new products to our website at www.opensystems-publishing.com/vendors/submissions/np/ and submit press releases at www.opensystems-publishing.com/news/submit. OSP reserves the right to publish products based on editors' discretion alone, and does not guarantee publication of any product entries.

Advancing Today's Technology Into Tomorrow

We specialize in completely reconfigurable and reprogrammable Digital FPGA and Analog FPAA PC/104 Boards.

We're Your Project's Solution.

www.jacyltechnology.com

RSC# 11 @www.mil-embedded.com/rsc

# **Board vendor FPGA toolkits make** or break your project

By Mark Littlefield

FPGAs dramatically accelerate DSP designs while bringing reconfigurability to the battlefield. But to wring out performance, ease-of-use, and overall program benefits, a design toolkit is needed. Better choose wisely.

Increasingly, the military community is recognizing that there is a class of signal processing that is now best accomplished via a reconfigurable computing implementation instead of the traditional method of software running on microprocessors. Modern Field Programmable Gate Arrays (FPGAs) have reached a level of density, speed, and cost such that system designers can now often achieve a tenfold reduction in size and power when compared with the traditional microprocessor-based approach. power of FPGAs stems from the opportunity to parallelize operations that a microprocessor must do sequentially.

For many signal processing designers, the question is not whether the use of FPGAs will result in higher performance – performance/power/cost – but whether the R&D investment will pay off. The simple fact is that developing signal processing functions in FPGAs has high technical risk, which can result in cost and schedule overruns.

When selecting a COTS board level product, a system integrator should be aware that the board vendor FPGA supporting toolkit will play a large role in reducing (or not) this technical risk. Herein, we will acquaint the reader with the nature of such tools and their effect on the cost of developing an FPGA compute solution.

#### What is an FPGA toolkit?

In our context, an FPGA toolkit is the collection of supporting IP (VHDL designs) and other *software* components that are offered for use by the vendor of

a board level product. We are not talking about the synthesis and simulation tools that are the domain of the FPGA silicon vendors and other tool specialists.

The components of an FPGA board toolkit fall into four categories:

- IP designs to control hardware features, for example, an SDRAM controller

- IP infrastructure to connect IP blocks together

- Software for system services, data movement, and general system integration

- Simulation and test

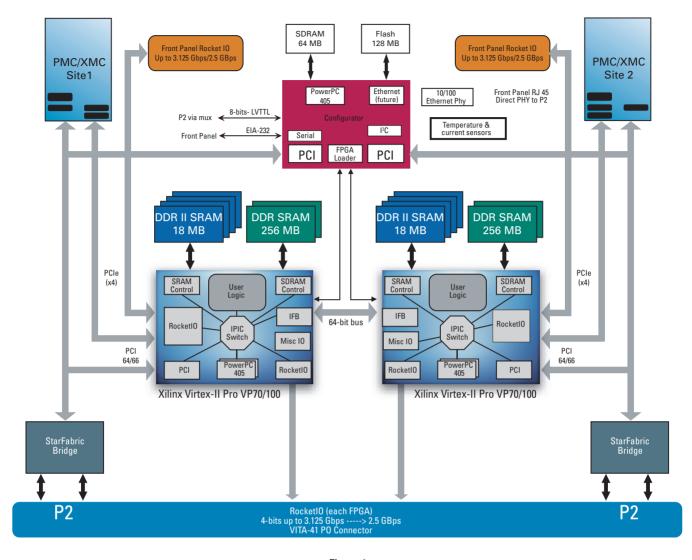

To appreciate the key attributes of these toolkit components, consider the Curtiss-Wright CHAMP-FX, an FPGA processing board designed for military signal processing applications. The CHAMP-FX, illustrated in Figure 1, integrates the Xilinx Virtex-II Pro FPGAs (VP70/100) with local memories, PCI interfaces, and high-speed serial interfaces.

The combination of DDR SDRAM for bulk storage and DDR SRAM for fast, nonsequential storage of algorithm data allows flexibility in mapping algorithms to this architecture. In a typical application,

data may first flow into SDRAM with intermediate storage in SRAM for algorithm processing with results output via the PCIbus to StarFabric or an alternate interface provided by a PMC module. In such dataflow architectures, the performance and ease of use of the memory controllers can dictate the overall performance of the application.

#### Robust IP blocks are critical

Implementing a memory controller provides an example of the criticality of the design kit to the success of a project. While it is possible to obtain *free* designs for an SDRAM controller from FPGA vendors, be advised that these are often limited-function reference designs. Experience has shown that it takes many man-months of experienced FPGA designer time to implement a high-performance, reliable SDRAM controller for FPGA-based hardware. The challenges that emerged – not unexpected – emanate from classic FPGA design issues. Examples of some of these design issues follow:

During the read cycle of a DDR SDRAM, the FPGA sends out a clock to the SDRAM and waits two cycles for a four-word burst to return. The challenge is in clocking the data back from the SDRAM. There is skew between the

Figure 1

transmitted clock and the data (due to 180 ps/inch PWB trace delay), so this is not an optimal approach to use. A better approach is to use a phase-shifted clock within the SDRAM controller IP that can account for the PWB trace length and transmission characteristics. This allows the FPGA to clock in read data with the appropriate timing margins. Because the FPGA SDRAM controller is working with externally connected devices, the design must take into account the specific FPGA pins used for the interface, the placement of the controller within the FPGA, and the PWB track lengths. At the 132 MHz operating frequency of the SDRAM interface, there is the narrow 2-3 ns window during which the data is valid. Debugging the interface between FPGA and memories is further complicated by

modern BGA packages that preclude the use of oscilloscopes and logic analyzers. If it is not working, it is very difficult to diagnose the cause of the problem.

FGPA designs must adhere to simultaneous switching output rules. When too many outputs from a particular bank switch at the same time, noise is introduced into the system, which can cause data errors to occur. This is another subtlety of FPGA IP design that is difficult to debug because the errors are somewhat random and analog in nature.

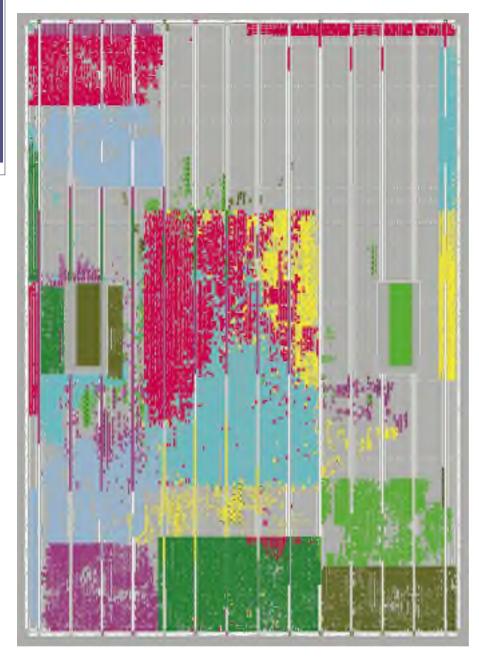

There is significant effort required to get a memory controller to function correctly. Getting controllers to work at high speeds (200 MHz SDRAM, 132 MHz SDRAM) also requires particular attention be paid to the placement of the IP blocks within the FPGA. A robust design optimized for a particular hardware implementation will include carefully selected and tested constraint information that ensures that the complete design, when integrated with the user's logic, will continue to operate within timing requirements. Figure 2, a sample floorplan, shows an example of the placement of IP blocks that have been constrained to particular placement within the FPGA. This is taken from the Xilinx ISE floor planning tool. The colors represent different IP blocks. The constraint files tell the placement tool to place all the logic for a given block within a certain area. This helps ensure repeatable timing within the block and makes it less sensitive to the logic the user is adding.

Figure 2

Last but not least is the added challenge presented by the wide temperature ranges encountered in military applications. The typical environmental requirement of -40 °C to +85 °C translates to an even wider range of -40 °C to +110 °C for the silicon. The design tools provide estimates of the timing effects over temperature, but only costly environment testing can verify the real effects, which will rarely be exactly as predicted. The design kit IP, if prequalified to this temperature, removes this as a risk item.

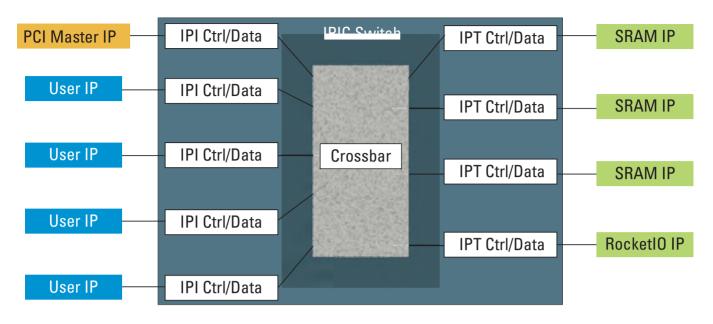

#### Interconnecting IP blocks

It is desirable for IP controllers and functional blocks provided as part of a toolkit to adhere to a consistent interface standard. Common interfaces ease IP block integration. We have adopted two interface conventions defined by Xilinx, IP Interconnect (IPIC) and Local Link. Memory mapped interfaces adhere to the IPIC standard, allowing an IP block to read or write to a memory address or register. SDRAM, SRAM, and the PCIbus are provided with IPIC interfaces.

Local Link is a packet-oriented interface for streaming data applications. In a DSP application, it is common for sensor data – digitized RF, electro-optical, and sonar – to arrive in nonaddressed packet form. The RocketIO controllers (3.125 Gbps) are supported with Local Link interfaces and DMA controllers to direct streaming data into memory-addressed locations.

To simplify the interconnection of user IP with the toolkit IP modules, the company has developed an IPIC switch, which allows modules with IPIC or Local Link interfaces to connect together seamlessly (see Figure 3). Multiple IPIC switches can be instantiated in the design, allowing users flexibility in choosing the best solution.

# Simulation: Don't take it for granted

FPGA signal processor designs are complex and, unlike software, are not easily instrumented for testing purposes. (There is no printf()!) The rule of thumb for a complex project is that simulation is 50 percent of the effort. It is fairly obvious that the FPGA vendor simulation tools can simulate the logic within the FPGA, but unless models are provided for external devices connected to the FPGA, the simulation cannot include interaction with these devices. A good FPGA toolkit will offer a test-bench environment that includes models of all the external interfaces, the capability to initialize memory interfaces and pass data from PCI and RocketIO into the FPGA and check memory, and the capability to test PCI or RocketIO data against expected data previously stored in files. The toolkit should provide a scripting language to facilitate the simulation of the design with test data and the capture of output data into files for comparison against expected results.

Unless a good simulation environment is part of the toolkit, the customer will be faced with a great deal of unplanned effort to establish a test environment. Figure 4 depicts the simulation models that are supplied with the CHAMP-FX design kit, and the logical points where data can be input or output from the simulation.

Figure 3

The final stage of testing requires loading and running the logic on the target hardware and integrating the design with the rest of the system. Despite efforts to accurately simulate a design, there remains a possibility that it will not work as intended. The Xilinx Chipscope logic analyzer is a great tool to probe the internals of a design in real time and to deduce where a problem resides. The use of Chipscope, however, requires some support within the FPGA toolkit to simplify including it in the design, so a

prospective customer would be advised to check into its support. Once the FPGA bitstream design is stable, the integration effort is eased by the availability of a rich set of software APIs for device control, data movement, and interprocessor synchronization.

The quality and coverage of the FPGA toolkit that accompanies a COTS FPGA board is critical to the schedule and cost of an FPGA-based project. Since FPGA toolkits are like software in some respects,

File driven simulation data Rocket10 Model Points of comparison of simulation versus expected result Intra-FPGA **SRAM** bus Model Models **FPGA** PCI Model **SDRAM** Models Clock Generation Model

Figure 4

the quality, performance, and functionality can take some extra effort to ascertain. This extra time is well spent, since any one of the issues discussed herein could result in many man-months to resolve.

Mark Littlefield is the product marketing manager for Curtiss-Wright Controls Embedded Computing's FPGA computing

product line. He has more than 15 years of experience in the embedded computing industry, first as an engineer developing robot vision systems for NASA, and later as a field applications engineer, technical program manager, and product manager. Mark has a BS and an MS degree in Control Systems Engineering from the University of West Florida.

To learn more, contact Mark at:

# **Curtiss-Wright Controls Embedded Computing**

741-G Miller Dr. SE Leesburg, VA 20175 Tel: 703-779-7800 Fax: 703-779-7805

E-mail:

Mark.Littlefield@curtisswright.com Website: www.cwcembedded.com

# Design strategies for an FPGAbased 256-channel digital down converter

By Rodger H. Hosking

FPGAs can replace traditional ASIC-based digital down converters in high channel count Software-Defined Radios. Their inherent parallelism allows multiple digital receiver channels per chip, and available COTS IP cores can be used to realize up to 256 independently controlled channels in a Xilinx Virtex family FPGA.

As Software-Defined Radio technology further penetrates large communication systems for battlefield military radio networks, commercial wireless systems, manned and unmanned aerial vehicles, and monitoring facilities for SIGINT and COMINT, the need to accommodate a large number of agile frequency channels for radio receivers is quite apparent. In each of these applications, the same critical metrics apply: size, weight, power, and cost for each receiver channel.

Traditional Digital Down Converter (DDC) ASIC devices feature only one to four channels per chip, and straightforward implementations of DDCs in FPGAs consume a significant percentage of available resources. A new approach to DDC design takes advantage of the parallelism of FPGAs to create a highly efficient architecture for multichannel receivers.

#### **Basics of digital down converters**

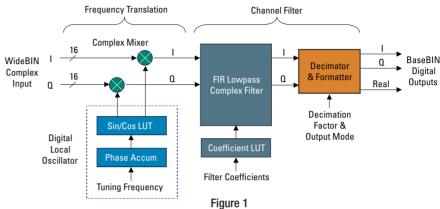

DDCs, often called *digital receivers*, perform the two essential software radio functions: frequency translation and channel filtering. In a basic DDC shown in Figure 1, a mixer and local oscillator perform the frequency translation.

The local oscillator consists of a digital phase accumulator that advances each clock by a programmable increment equal to the tuning frequency. The phase accumulator is a register whose full-scale value represents 360 degrees of a sinusoid. A sine/cosine lookup table converts the phase angle of the accumulator to the digital voltage value of the sinusoid. The higher the increment, the faster the phase accumulator steps through the sine table. It naturally overflows at the top, preserving any residue left in the register as a phase offset for the first sample of the next cycle. As a result, the output sinusoid is directly proportional to the phase increment or frequency setting. This block is a classic Numerically Controlled Oscillator (NCO), also often called a Direct Digital Synthesizer (DDS).

The mixer consists of two digital multipliers that accept complex sine/cosine outputs from the local oscillator and digital samples of the receiver input signal produced by an A/D converter. Multiplication in the time domain produces a sum and difference signal in the frequency domain. If the local oscillator is set to the frequency of the input signal of interest, the difference term will be that input signal translated down to 0 Hz. Since the mixer is complex, the upper and lower sidebands of the input signal will be translated to negative and positive frequencies centered at 0 Hz.

The filter is a complex low-pass digital filter with two parallel I and Q arms whose coefficients are programmed for a pass band equal to the channel bandwidth. Because the output of the filter is bandlimited, the output decimation stage can drop the sampling rate accordingly.

DDCs are grouped into two main categories. Wideband DDCs have output channel bandwidths typically above 1 MHz and are appropriate for wideband Code Division Multiple Access (CMDA) and radar applications. Narrowband DDCs with bandwidths below 1 MHz are widely used for Frequency Division Multiplexed (FDM) systems including voice and music channels for telecom and commercial broadcast systems. While the mixer and local oscillator sections are quite similar for all DDCs, the best filter design depends on the filter bandwidth. For wideband channels, a conventional FIR filter is best (as shown in Figure 1). For narrowband channels, a multistage Cascaded Integrator-Comb (CIC) filter followed by an FIR to correct frequency droop is more efficient.

For narrowband applications, both ASIC and FPGA Intellectual Property (IP) cores are available using CIC filter designs.

# Annapolis Micro Systems The FPGA Systems Performance Leader!

SIGINT ELINT Digital Receivers FLIR

FOPEN Radar Systems Software Defined Radio

High Performance

Signal Processing in

Scalable FPGA Computing Fabric

Real Time, Real World.....REAL FAST!

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

Commercial ASICs feature as many as four channels per chip, like the popular Texas Instruments/Graychip GC4016.

IP core DDCs, like the LogiCore DDC from Xilinx for its Virtex-II Pro, can be scaled for various levels of Spurious-Free Dynamic Range (SFDR) performance to use more or less of the available resources. For example, a complex DDC with 84 dB SFDR consumes approximately 1,700 slices. In a mid-sized FPGA device with 24,000 available slices, only about 14 DDC channels can be accommodated. For applications requiring several dozen or even hundreds of channels, this approach can become impractical.

#### Channelizers

Because of the extremely fine resolution of its NCO tuning frequency, a true DDC can translate any input frequency component down to 0 Hz, often with 32-bit accuracy. This ability makes DDCs ideal for applications that require precise changes in tuning such as in continuous Doppler correction for satellite tracking systems.

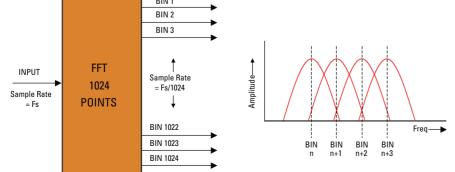

However, in other applications, a *channelizer* approach may be sufficient. This is a bank of equally spaced, fixed frequency band pass filters whose outputs are translated to baseband (0 Hz). One crude example of a channelizer familiar to everyone is a simple FFT. It converts a block of N time samples equally spaced in time into block of N frequency samples equally spaced in frequency. For a continuous stream of input time sample blocks, samples at a given point in successive output blocks represent a translated, band pass frequency signal or *bin*.

By selecting the output of a particular bin, a channelizer can serve as a primitive DDC, but with extremely coarse tuning resolution determined by the number of points in the FFT, as shown in Figure 2.

Another serious limitation of the FFT as a DDC is the frequency response (pass band flatness) of the bin, and rejection of energy from adjacent bins (stop band rejection). Other channelizer designs use various digital filtering techniques to split the bands with better flatness and adjacent channel rejection, but they usually require significantly more hardware than an FFT for a

comparable number of bins. Regardless of its design, the tuning resolution of any channelizer is simply equal to the number of bins or channel filters. As a result, channelizers may be useful for spectrum analyzers, scanners, and energy survey equipment but they are rarely used as substitutes for DDCs in software radio communication systems.

#### **Rethinking the multichannel DDC**

The software radio market generates a growing number of requests for DDC solutions with densities higher than the 16 or 32 channels provided per board using ASICs or standard FPGA designs. Therefore, we embarked upon a mission to develop a signal processing architecture for a narrowband DDC with 64 channels or more, with full tuning resolution, but with much more efficient use of FPGA resources than deploying a farm of conventional DDC cores.

Each conventional DDC requires its own local oscillator (phase accumulator and sine table), mixer (two multipliers), and FIR filter (multipliers and accumulators). All of this hardware must operate at the full input sample clock rate, and clock rates for A/Ds commonly used in software radios range between 100 and 200 MHz. Since this is the same clock range rating for commercial DDC IP cores, all of the hardware resources used for each channel must be dedicated to that channel.

However, imagine that the input data sample rate is reduced by a factor N. By operating the DDC hardware resources required for one channel at the full clock rate, those same resources can then be multiplexed (time shared) across N channels. Of course, provisions must be made for buffering the data for all channels while multiplexing. This is usually done in RAM or in delay memory, a common feature in FPGAs.

One way to achieve this input rate reduction is to split the input signal into a bank of N adjacent frequency bands using a channelizer. Then, the output sample rate for each band can be reduced by a factor of N. The output from the band containing the signal of interest can be selected as the input to any given DDC to fine tune within that band.

The tradeoff question becomes: Are the resources freed up by

multiplexing the DDCs more than the resources required for the channelizer? The answer lies in how efficient the channelizer can be.

Figure 2

#### Realizing the design

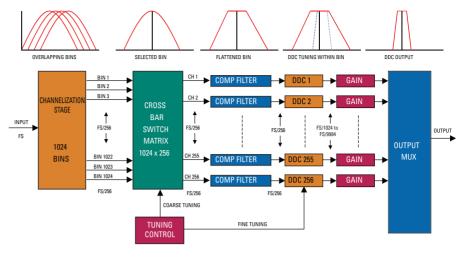

Figure 3 shows an FPGA-based 256-channel DDC IP core that combines a channelizer stage with a multiplexed DDC stage.

The crucial part of this design is the channelizer stage. It accepts a single wideband input stream and delivers a channel bank of 1,024 output bands equally

spaced in frequency, but with significant overlap between adjacent bands.

The output sample rate of each band equals the input sample rate (Fs) divided by 256, rather than 1,024, as would be expected with a simple FFT. In fact, inside the channelizer are four high-speed 1,024-point FFTs running in parallel using a proprietary windowing and overlap processing technique. The outputs of the four separate FFTs deliver samples at a rate of Fs/1024. These outputs are combined to form a single output at a sample rate of Fs/256, supporting the wider bandwidth that will sufficiently overlap adjacent bands.

Figure 3

The next stage is a crossbar switch matrix that accepts 1,024 edge of to inputs from the channelizer and delivers 256 outputs, one to each DDC channel. The switch is nonblocking so that any of the 256 outputs can be independently sourced from any of the 1,024 channelizer bands with no restrictions.

Since the

Each of the 256 channels is tuned by a separate 32-bit frequency word, with the most significant bits sent to the switch matrix for coarse tuning. This selects the correct channel band for each channel. The least significant bits of the frequency word are used by the DDC stage for fine tuning within the selected band.

Because the channelizer outputs exhibit frequency droop at the band edges, a fixed compensation FIR filter flattens the pass band to within 1 dB across a span equal to twice the band-to-band spacing.

A bank of 256 independently tuned DDC sections, each with its own local oscillator, mixer, and FIR filter, processes the 256 compensated switch matrix outputs. Because the channelizer has dramatically reduced the input sampling rate to each DDC section by a factor of 256, the DDCs are implemented using highly multiplexed hardware resources and block RAM to preserve the data for each channel. A gain stage, output multiplexer, and data formatter complete the design.

#### **Performance and tradeoffs**

The maximum output bandwidth of this design equals the channelizer band-to-band spacing of Fs/1024. For an input sample rate of 100 MHz, this spacing is about 100 kHz. And because of the broadened response, each channelizer output has a clean pass band equal to twice the band spacing, or about 200 MHz.

This allows the DDC to perform fine tuning by sliding its local oscillator frequency  $\pm$  100 kHz across the selected 200 kHz channelizer band to precisely center the DDC output. Choosing a wider DDC output bandwidth would restrict the DDC tuning

range, since the edge of that wider bandwidth would cross the edge of the flat, spurious-free region of the channelizer output.

Samples of the translated signal from the mixer arrive at the decimating FIR at the channelizer output sample rate of Fs/256. Since the maximum available DDC output bandwidth is Fs/1024, the lowest decimation factor allowed in the FIR is 4.

RSC# 19 @www.mil-embedded.com/rsc

#### Hardware—RECONFIGURABLE FPGAS

For narrower output bandwidths, the maximum decimation factor is determined by the complexity (number of taps) of the FIR filter, which must perform at least as well as the channelizer filter in order to maintain that dynamic range of 75 dB. Choosing a reasonable number of multiplier/accumulator stages yields an FIR filter suitable for decimation factors from 4 to 39 in steps of 1. The number of filter taps is equal to 26 times the decimation factor of the filter.

Since the channelizer decimation (256) and FIR filter decimation (4 to 39) multiply, the overall range of decimation range for the entire core is 1,024 to 9,984 in steps of 256. Each of these 36 available decimation factors requires its own set of filter coefficients, which are stored in a table within the FPGA. For an input clock of Fs = 100 MHz, the range of output bandwidths using the default 80 percent filter characteristic is approximately 8 kHz to 80 kHz. For any decimation setting, the overall DDC channel characteristics, including the channelizer response, are shown in Figure 4.

Because of the multiplexed DDC hardware, all 256 channels must have the same decimation factor setting. For high-channel count systems, this limitation is usually not an issue since it is quite common for all such channels to have the same bandwidth.

Overall performance of the complete 256-channel FPGA-based DDC IP core includes a spurious-free dynamic range of 75 dB, a pass band ripple of 0.4 dB, a pass band edge droop of 1.0 dB, and frequency tuning resolution of Fs/2<sup>32</sup>. The maximum clock frequency depends on implementation details, but can be as high as 185 MHz in a Virtex-4 FPGA with speed grade 12.

The core consumes approximately 18,000 logic slices of a Virtex-4 device, compared to 1,700 slices for a single channel DDC LogiCore reference design. Although there are some limitations in decimation factors and dynamic range, this new core represents an improvement in the channel-per-slice ratio by a factor of more than 20.

Figure 4

This 256-channel DDC core is available as a member of the GateFlow IP Core Library suitable for use with any Virtex-II, Virtex-II Pro, or Virtex-4 product.

For customers preferring to avoid FPGA development, it can be ordered as a factory

installed option to the Pentek Model 7140 Dual Transceiver PMC module (shown in Figure 5) where it occupies approximately 76 percent of the Virtex-II Pro XC2VP50.

Figure 5

In order to keep pace with a steady flow of new FPGA device offerings, designers must continually evaluate, and often reinvent, real-time embedded computing strategies for critical military and commercial applications. Armed with a detailed understanding of new device resources, creative engineers can often approach a tough problem from a radically new angle to gain a major advantage. While many new FPGA design tools offer impressive features and improved efficiencies, these truly significant leaps in FPGA performance usually come from inspiration, not from automation.

Rodger H. Hosking is Vice President and Cofounder of Pentek, Inc., where he is responsible for new product definition, technology development, and strategic alliances. With more than 30 years of experience in the electronics industry, he has

authored hundreds of articles about digital signal processing. More than 10 years ago, Rodger introduced digital receiver technology to the government electronics industry through numerous presentations and his widely read publication The Digital Receiver Handbook. Prior to his current position, he

served as Engineering Manager at Wavetek/Rockland and holds patents in frequency synthesis and spectrum analysis techniques. He received a BS degree in Physics from Allegheny College in Pennsylvania and BSEE and MSEE degrees from Columbia University in New York.

For more information, contact Rodger at:

#### Pentek, Inc.

One Park Way

Upper Saddle River, NJ 07458 Tel: 201-818-5900, Ext. 228 E-mail: rodger@pentek.com Website: www.pentek.com

# ENGINEERED LIKE NO OTHER

FROM CONCEPTS TO DEPLOYMENT

# V394 "MAVERICK" Ultra High Performance, Dual PMC, PowerPC VME SBC

- · Dual 7447A/7448 PowerPC up to 1.2GHz

- · Up to 1MB of L2 Cache

- · Full Symmetric Multi Processing (SMP) support via Discovery®-III

- 128-bit AltiVec™ technology support

- · Dual 64-bit 66/100MHz PCI-X local buses

- Up to 1GB of 333 MHz DDR SDRAM via SODIMM modules

- Two 64-bit 66/100MHz PMC expansion sites, one with rear I/O

- · Ultra SCSI 160 with differential output

- · Three Gigabit Ethernet ports

- · Dual USB, IDE DMA-100, Serial, PS2 Mouse and Keyboard

- · 32MB of application Flash

- · One Multi Protocol Sync/Async Serial port

- · 2MB of Bootable Flash

- Onboard 2.5 inch IDE Hard Disk Drive (Optional)

- Parallel port and 21 discreet digital I/O lines

- Optional triple 66MHz, 64-bit PMC expansion module

- Supports VME-64 via Tundra Universe-II®

- · Support for 5-row or 3-row VME card cages

- · Front panel LEDs for POST code and Status display

- · Support for VxWorks®, Linux® and QNX® Operating Systems

#### CC61X "ROCK"

High Performance, 3U Conduction Cooled, Rugged CompactPCI Pentium® M SBC

- · Up to 1.4GHz Pentium® M processor with up to 2MB of L2 Cache

- · Ultra-low power requirements as low as 12W Max

- · Up to 2GB of 266MHz DDR SDRAM

- · Up to 16GB of Bootable Flash memory

- Baseboard Management Controller (BMC) to meet PICMG2.9

- Full Health reporting and monitoring with extensive BIT/EBIT

- Dual Gigabit Ethernet ports with TCP/IP Offloading Engine

- Dual Video to support DVI and RGB

- Full Power Management control:

- ACPI 2.0 compliant (Suspend to memory/disk etc.)

- Geyserville® III support (Speed and Voltage stepping)

- Support for battery operation and standby power

- · Four USB-2.0 ports, two Serial ATA and two Serial ports

- 512KB of BIOS/user Flash and 2Kb of Serial EEPROM

- · RTC with onboard and external battery support

- High speed I/O via SAM™ bus expansion connector (PCI-X or AGP)

- Available in standard 0-55°C or extended temperature -40° to +85°C

- Onboard heaters allow extended low temperature storage/operation

- · Support for Windows® XP/2000, VxWorks® and Linux®

LEADING THE EMBEDDED MARKET SINCE 1979.

PERFORMANCE, RELIABILITY, LONGEVITY

#### GENERAL MICRO SYSTEMS, INC.

TEL(800) 307-4863 • gms4sbc.com RSC# 21 @www.mil-embedded.com/rsc

GENERAL MICRO SYSTEMS, INC. REGISTERED TO ISO9001 FILE NUMBER A8073

# **SDR and JTRS: Lessons learned**

# An interview with Col. Steven MacLaird, USAF (ret.) and former Program Executive Director of the Joint Tactical Radio System JPO

#### **EDITOR'S FOREWORD**

Col. Steven MacLaird managed the Joint Tactical Radio System (JTRS) Joint Program Office (JPO) from 2000 until his retirement from the U.S. Air Force in 2005. JTRS is one of the DoD's largest programs, which I include with the "big three" of the Joint Strike Fighter F-35 and Future Combat Systems. Last year, I estimated that over the program's life, somewhere between \$12-\$15 billion would be spent on JTRS radios and infrastructure (download available at http://meecc.com/presentations/CIUFO.pdf).

Steven successfully navigated a challenging program, rife with technical, financial, and programmatic obstacles. Today, the JTRS clusters have been renamed and shuffled around, and the program is realigning its timetable for initial deployment over the next 12 months. He has been selected to sit on the board of directors of PrismTech, a COTS supplier of the Software Communications Architecture (SCA) that's essential to JTRS. I had the privilege of speaking with him last April. Edited excerpts from that conversation follow. – Chris Ciufo

MIL EMBEDDED: Please provide a brief overview of the current JTRS radios and explain how they relate to the previous clusters.

**MACLAIRD:** In March of last year a hand off was initiated between the old [Joint Program Office] organization and the new, and I went in and briefed Dennis Bauman on the program. And we provided to him a way ahead on the organizational structure. He's adopted a large set of that, which you have undoubtedly seen in the press.

The ground domain consists of Ground Mobile Vehicles (GMV) radios and the Handheld/Manpack/Small form fit (HMS) radios, i.e., *Cluster 1 and Cluster 2*. Special radios used to be *Cluster 2*, also known as JTRS Enhanced MBTR (JEM). The airborne maritime fixed site domain is made up by the AMF program, which previously, probably about November 2004 was to be the airborne fixed site program, known as *Cluster 3* and *Cluster 4*, and the Air Force and Navy came together and consolidated them into the AMF. Finally, the waveform and crypto program was transitioned into the Network Enterprise Domain (NED).

MIL EMBEDDED: Why did you recommend changing the clusters around?

**MACLAIRD:** There was a strong service equity issue within the program when I took it over in June of 2001, which led to some dysfunctional approaches to delivering capabability to the joint force. Also, when you looked at the history of the original intent

of the program organization, the organization that I inherited did not reflect the intent of the program.

MIL EMBEDDED: Can you define the term service equity?

**MACLAIRD:** The way the money was laid out – actually, the way the program was laid out – was the funds for the particular programs resided in the service's top line [budget]. So if you talk about what used to be Cluster 1, that was predominately Army funded. The Army ran that program. And although the JPO director had oversight authority over the program, the actual funding went through the Army, then through the JPO and separately through the Army CECOM for Cluster 1. And the leadership of the organization reported through another organizational structure up at [U.S. Army] CECOM.

MIL EMBEDDED: Let's talk about some of the technologies. Can you comment on COTS technology and this program ... where it's come from to where it is today?

**MACLAIRD:** *Proprietary* is a pretty good summation of the program. What's really important to understand is that you took a program that started in 2000 that not only was trying to build hardware but software operating systems and waveforms, *and* build new standards *and* try to deliver new capability all at once.

What we can do today on FPGAs, GPPs, and DSPs and what people thought we could do back in 2001 when I took over the program has greatly expanded. Spectrum Signal [Processing], Harris Corporation, and General Dynamics are out there running

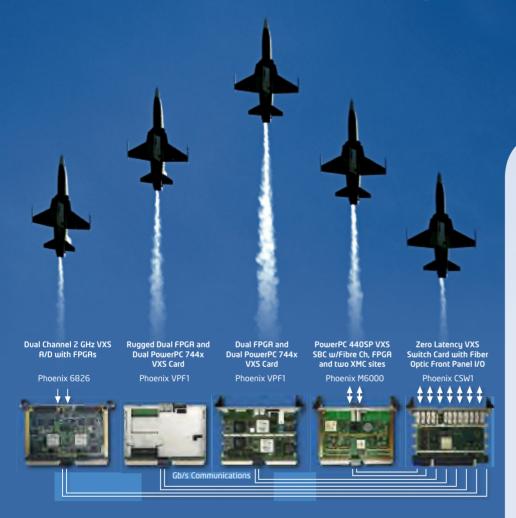

# **Coordinated Performance**

with Phoenix Systems

Real-Time Multi-Processors with High-Speed Serial Communications

#### Powerful

- Customer programmable Xilinx FPGA compute engines

- Multiple PowerPC processors

- Multi-channel Gbit/sec backplane communications

- Fiber Optic Front Panel I/O, including Serial FPDP

- High-speed Analog and Digital I/O

#### **Flexible**

- Combine FPGA and PowerPC Processors to match the application requirements

- Boards or complete sub-systems

- Open standards including VITA 41/VXS and VITA 42/XMC

- Air-Cooled to rugged conductioncooled versions

#### Innovative

- Zero Latency Switch technology

- TransComm<sup>TM</sup> inter-processor communications suite for simplified application development

Processing and FPGA

Input/Output

Data Recording

Bus Analyzers

For more information, please visit processor.vmetro.com/phoenix or call (281) 584 0728

# Software—software-defined radios (SDRs)

with the capability. So if you look at that and what technologies are out there, you know that open architectures with POSIX corporate middleware are critical.

Also, in February 2004 I spoke with NASA and they're now adopting the SCA. They actually had been looking at building their own standards and looked at ours and did a 168-page summary that said, bottom line: It's already here; we just have to adapt it for a space-based environment. They told me in 2003/2004 that they had four satellites waiting for proprietary software to show up so they could go launch the systems.

MIL EMBEDDED: What sort of technologies do we need going forward to actually bring JTRS into deployable fruition?

**MACLAIRD:** Our biggest challenge is in the processing because of heat and the issues of quickly and efficiently dissipating that heat. In the past, we've done that with size and with fans, which is not the best way to operate radios in desert environments. Balancing environmental factors plays a big part in how you design and deliver capability to the war fighter. But that's not the only place where JTRS technology needs to be focused.

Other system needs include focusing on new battery and antenna technology, smaller, lighter, more capable, and relying on easy access to commercial markets. I've seen needs in the

Special Operation Forces where they desire more batteries that are easily accessible (AA batteries, for example), and how do you do that – by going into a local Iraqi CVS or grocery store? War fighters are asking, "Why can't you build me a military radio capable of accepting commercial battery sources? And by the way, I want it to operate for 8 to 10 hours without taking out the batteries."

Also, JTRS radios have to talk to satellites, so we need transmit power and some proprietary [military] technology, but the radios still need to be reduced in size and weight. And we also need faster [red/black] encryption security chips – the ability to encode and decode and process information factors into the heat and battery issue, too.

MIL EMBEDDED: So what do you think the software impediment is in JTRS?

**MACLAIRD:** From my perspective of watching how we do things in government, the issue has to do with the program pace. You go in, you buy a capability, and you want to build it in 36-42 months. By the time you get there, things have changed.

We're talking about SDR, with the emphasis on *software-defined* and yet every conversation we have in the marketplace is about the hardware. A lot of people don't get the fact that the value

content in the future of these radios is going to be all software. Software needs to be produced very efficiently and, until now, that has been very difficult to do because open standards such as the SCA have been evolving.

MIL EMBEDDED: Let's go down that path for a moment. So what's the current state of the SCA?

**MACLAIRD:** I understand that they recently released version 2.2.2, which is basically a debugged version of the SCA. Just prior to my departure, we had pulled a team of experts together from government and industry, people to attack current and future concerns. People like: Vanu's John Chapin and PrismTech's Dom Paniscotti and Jerry Bickle, Spacecoast Communications President John Bard, and Lee Pucker of Spectrum Signal along with some others. We had laid out a road map with what we called SCA 3.x that would allow fixing of some of the problems of SCA 2.2 and migrate to a capability for above 2 GHz [RF]. And it also addressed a high-order language that some call *Modem HW Abstraction Layer* (MHAL). It created a similar higher order language or higher order abstract language capability that would allow the migration and maturation of the program.

We're talking about SDR, with the emphasis on software-defined and yet every conversation we have in the marketplace is about the hardware.

MIL EMBEDDED: I would argue that the idea behind the SCA core framework was a good one, but here we are four years later and we're still not actually shipping JTRS. Are we going down the right path with SCA?

**MACLAIRD:** As you go through any process, the issue is getting it to be socialized with the right people and adopted. There are a lot of people who have problems with opening up the architecture because they have proprietary solutions. PrismTech's view is that there is nothing fundamentally wrong with SCA. The 2.2 version does the job for which it was designed: The JTRS program provides radios, a common standard that has been reviewed and endorsed by the 130+ member Software Defined Radio Forum (SDRF) and the 880+ member Object Management Group (OMG). Both of these are well known standards bodies.

MIL EMBEDDED: If the military had to do this all over again, what do you think that this program should do differently, knowing what you now know?

**MACLAIRD:** Organization and financial structure were, in my mind, the biggest obstacles. Technology was there or would have evolved to get us to where we needed to be.

MIL EMBEDDED: Are there any technology issues that, if done differently, might have achieved more success sooner?

**MACLAIRD:** I would not have put the majority of the waveforms on a single contract. We put 20 or 21 Waveforms (Wf) on the contract with Cluster 1, and it became a big output to manage

when the contract focus and difficulties seemed to be more on the hardware. I think if the organizational and financial structure and political structure had been set up right, more along the lines of what it is today, we could've been more successful than we were.

Col. Steven MacLaird (USAF ret.) served as Program Director of the U.S. Department of Defense's JTRS Program Office. His responsibilities included: development and acquisition of a new family of SDRs for joint use throughout the armed services with the goal of replacing 750,000 radios in the 2 Mhz to 2 GHz radio spectrum; coordinating the development of the radio SCA into commercial and international standards; the development of JTRS radio families to serve domestic and international uses as well as encouraging their commercial use; overseeing five Service cluster acquisition programs valued at more than \$9 billion. Steven is a 1978 distinguished graduate of Kansas State University's Reserve Officer Training Corps program.

For more information, contact:

#### **PrismTech**

6 Lincoln Knoll Lane, Suite 100 Burlington, MA, 01803 Tel: 781-270-1177

Fax: 781-238-1700

Website: www.prismtechnologies.com

RSC# 2501 @www.mil-embedded.com/rsc

# PENTXM2. Sizzling performance in a VME Blade that never loses its cool.

Looking for the best in high speed server class performance for embedded applications? Look no further than the PENTXM2 family of manageable single-board computers (SBCs)—only from Thales. It delivers the sizzling computing power your applications require while meeting the demands of thermally constrained environments.

Want power? PENTXM2 VME blade servers are ready for your most bandwidth intensive applications. At the heart of the system is a 1.67GHz Dual-Core Intel Xeon processor combined with an Intel E752O server class Memory Controller Hub (MCH). That translates to approximately twice the performance of previous single-core products.

Need flexibility? PENTXM2 VME Blades interface with a full range of standard

hardware via triple USB2.O, Dual SATA-150 and dual PMC slots. With PCI-Express available on the XMC slot or the rear PO interface you'll achieve even greater performance and flexibility. EFI Open Standard Firmware enables the card to boot Linux 2.6, VxWorks, Lynx OS, Microsoft Windows and Red Hat Linux operating systems. Desire real peace of mind? The extended lifecycles associated with the Intel Xeon processor and E 7520 chipset, along with

Thales' experienced, long-term support, is your guarantee of outstanding availability and a fully protected investment.

PENTXM2 VME Blades. Once again Thales sets the standard in real-time COTS system performance.

For more information please contact: Laurent Richard Tel: +33 (0)4 98 16 34 00

$e\hbox{-mail: infocom@thalescomputers.fr}\\$

The commercial delivery of the first generation of Software-Defined Radios has shown that the technology is viable and scalable. In order to push into new markets and domains, Software-Defined Radio must meet the challenges of security, safety, and a smaller footprint.

As the first wave of Software-Defined Radios (SDRs) built for compliance with the U.S. Military's Joint Tactical Radio System(JTRS)SoftwareCommunications Architecture (SCA) becomes available, radio manufacturers continue to increase their use of COTS tools. Their goal is to reduce development and deployment costs while enabling more design options throughout the engineering process. Commercial companies are looking to leverage this substantial investment in technology and tools, in order to extend SCA-based SDRs to new domains and to new types of devices.

Various groups see SDR as a solution to these needs. The military needs *smart radios* that can flexibly work in whatever country they are deployed, since they may be interacting with local forces on different networks. Cell phone makers need to consolidate the multimode radios they are building into their handsets and provide bug fixes with downloaded software. Public safety officials need a way to enable interagency communications problems during a crisis.

# The next advancements in Software-Defined Radio

By Joseph M. Jacob

### **SDR** defined

#### What is Software-Defined Radio?

In an effort to improve upon the flexibility, usability, and extensibility of radios, a variety of companies have been working for almost 20 years to create radios where the core functionality is implemented in software rather than hardware. A Software-Defined Radio (SDR) is a radio in which 100 percent of the modulation and demodulation is defined in software instead of being hardwired into the electronics. This means that the frequency band, performance, and functionality can be upgraded with a simple software download and update. In essence, an SDR is a radio that is substantially defined in software, with a physical layer behavior that can be significantly altered through changes to its software. SDR provides an efficient and comparatively inexpensive solution to the problem of building multimode, multiband, multifunctional wireless devices. An SDR is capable of being reconfigured to operate with different waveforms and protocols through dynamic loading of new waveforms and protocols. A waveform can contain a number of different parts: It may not be just *AM vs. FM* but also have security and safety characteristics built into the waveform itself. The figure below, courtesy of the Communications Research Centre of Canada, shows the steps in the Software-Defined Radio life cycle.

#### **SDR Development Lifecycle**

**Software Communications Architecture**

CZC

In order to achieve these goals, SDR technology needs to be further advanced to satisfy security, safety-critical, and footprint issues.

#### Security as a priority

Ensuring that radio communications are secure is one of the highest priorities for both military and commercial radio markets. In order for an SDR to be effective, the radio must implement robust security. In the military, security of communications on the battlefield is

simply a basic requirement. Without it, the radio is useless, even harmful.

Radio often provides the only means of communication in high-threat military environments. Unfortunately, military personnel have not yet been able to trust that radios will be effective at keeping multiple levels of classified and unclassified transmissions separate. They need to have confidence that secret communications on one channel intended for U.S. forces only will not bleed into

unclassified channels, or be compromised by hostile third parties. It is important to note that SDRs transmit not only voice but also data. Voice transmission becomes only a small part of the overall usage of SDRs.

Both in the military and commercial markets, wireless transmission of information will continue to grow. Whether browsing on the Web, transmitting video, sending private financial information, or simply sending E-mails, the data component usage of SDR is the most significant component, and the one that often requires the highest security levels.

For public safety, security of communications during a time of crisis is essential to ensuring that public responders can get their job done. In the commercial world, handheld cell phones or radios will be used to do a variety of different tasks, including speaking with friends, sending text or video messages to

colleagues, and communicating with the bank to engage in financial transactions. Consumer confidence in these devices will depend in large part on the level of security that they provide. If that device is accepting E-mail and instant messages while transmitting credit card and bank information, consumers will want assurance that subversive code contained in an E-mail or IM will not have any effect on their private financial information.

Virtually all Software-Defined Radios use a Real-Time Operating System (RTOS) as the core operating system for the radio. A remarkable amount of work has been done during the past five years in collaboration with the U.S. Air Force Research Laboratory and the National Security Agency to create highly secure versions of some of these RTOSs. The result of this effort is the Multiple Independent Levels of Security (MILS) architecture (www.mils.us). The MILS versions of the RTOSs are

called *separation kernels*. Currently, three different RTOS vendors have publicly announced separation kernels: Green Hills, LynuxWorks, and Wind River. Although the initial development and deployment of these separation kernels is for defense applications, there is growing demand for these high-assurance MILS separation kernels throughout commercial domains as well.

The core security functionality of the MILS architecture is to keep data separate and to control information flows on a highly secure basis. The core foundational communications middleware for MILS, the Partitioning Communication System (PCS), ensures that only authenticated and authorized parties are allowed to exchange data, that their communications are secure and unbreakable, and that communications of data from different domains are kept separate over just one communications channel.

# RTD Embedded Technologies, Inc.

"MIL Value for COTS prices"™

8000 MIPS dspModules<sup>™</sup>

| Geode cpuModules <sup>™</sup> |                                         |                        |                  |                  | Pentium <sup>®</sup> M cpuModules <sup>™</sup> |                 |                 |                 |                 |                 |                 |                 | 80              |                 |

|-------------------------------|-----------------------------------------|------------------------|------------------|------------------|------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|                               |                                         | Pentium <sup>®</sup> M |                  |                  |                                                | Intel® Celeron® |                 |                 |                 |                 |                 | AMD Geode       |                 |                 |

|                               | cpuModules <sup>™</sup><br>-40 to +85°C | CMX58886PX1400HR       | CMV58886PX1400HR | CMX58886CX1000HR | CMV58886CX1000HR                               | CME47786CX650HR | CME47786HX650HR | CML47786CX650HR | CML47786HX650HR | CMX47786CX650HR | CMX47786HX650HR | CME26686HX333HR | CME27686HX333HR | CME27686CX333HR |

|                               | AT Expansion Bus                        |                        |                  |                  |                                                | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |

| Bus                           | <b>PCI Universal Expansion Bus</b>      | ✓                      | ✓                | ✓                | ✓                                              | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |                 | ✓               | $\checkmark$    |

| B                             | PCI Bus Masters                         | 4                      | 4                | 4                | 4                                              | 4               | 4               | 4               | 4               | 4               | 4               |                 | 4               | 4               |

|                               | APIC (add'l PCI interrupts)             | 9                      | 9                | 9                | 9                                              | 9               | 9               | 9               | 9               | 9               | 9               |                 |                 |                 |

|                               | CPU Max Clock Rate (MHz)                | 1400                   | 1400             | 1000             | 1000                                           | 650             | 650             | 650             | 650             | 650             | 650             | 333             | 333             | 333             |

|                               | L2 Cache                                | 2MB                    | 2MB              | 512k             | 512k                                           | 256k            | 256k            | 256k            | 256k            | 256k            | 256k            | 16K             | 16k             | 16k             |

| S                             | Intel SpeedStep Technology              | ✓                      | ✓                |                  |                                                |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| and BIOS                      | ACPI Power Mgmt                         | 2.0                    | 2.0              | 2.0              | 2.0                                            | 1.0             | 1.0             | 1.0             | 1.0             | 1.0             | 1.0             |                 |                 |                 |

| 펄                             | Max Onboard DRAM (MB)                   | 512                    | 512              | 512              | 512                                            | 512             | 512             | 512             | 512             | 512             | 512             | 256             | 256             | 256             |

| an                            |                                         | ✓                      | ✓                | ✓                | ✓                                              | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |

| CPU                           | Nonvolatile Configuration               | ✓                      | ✓                | ✓                | ✓                                              | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |

| U                             | <b>Quick Boot Option Installed</b>      | ✓                      | ✓                | ✓                | ✓                                              | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |

|                               | Fail Safe Boot ROM                      |                        |                  |                  |                                                | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |

|                               | USB Boot                                | ✓                      | ✓                | ✓                | ✓                                              | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |                 |                 |                 |

|                               | Watchdog Timer & RTC                    | ✓                      | ✓                | ✓                | ✓                                              | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |

|                               | IDE and Floppy Controllers              | ✓                      | ✓                | ✓                | ✓                                              | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               | ✓               |

|                               | SSD Socket, 32 DIP                      |                        |                  |                  |                                                |                 | 1               |                 | 1               |                 | 1               | 1               | 1               |                 |